## **Sample Midterm Questions for ECE 329**

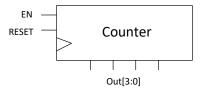

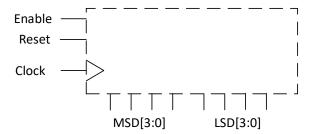

**Q1.** Using logic gates and two 4-bit counters shown below, design a two-digit saturating Binary Coded Decimal (BCD) counter that counts from 00 to 99.

It should have three inputs: clock, reset and enable. Name the outputs corresponding to the least significant BCD digit as LSD[3:0] and most significant BCD digit as MSD[3:0], i.e. you should design the circuit inside the dashed box using the counters given above

On each rising edge of the clock:

- If reset is a 1, your BCD counter should go to 00.

- Otherwise, if Enable=1, it should increment to the next value (staying at 99 if already at 99)

- Otherwise, it should hold its value.

- **Q2.** Implement the following Boolean functions with PAL:

- a. Find the corresponding minterms

- b. Draw the PAL programming table

- c. Draw the fuse map.

$$w = \sum (3,4,5,6,7,12,13,14,15)$$

$$x = \sum (6,8,9)$$

$$y = \sum (0,2,3,4,5,6,7,11,12,13,14,15)$$

$$z = \sum (5,6,8,9,13)$$

**Q3.** Design an asynchronous 3 bits down counter and a synchronous 3 bits up counter separately only using J-K flip flops in both (totally 2 separated counters will be designed). Then design a circuit that gives alert at any time when the outputs of these two circuits are exactly same.

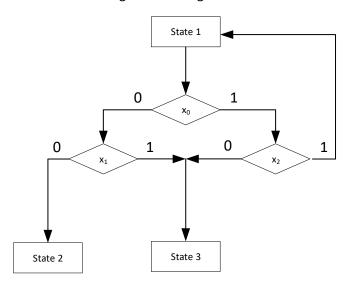

**Q4.** Draw the state table and the state diagram for the given ASM chart.

**Q5.** The outputs of four registers *R0*, *R1*, *R2*, *R3*, are connected through 4-to-1-line multiplexers to the inputs of a fifth register, *R5*. Each register is 8-bits. The required transfers are dictated by four timing variables  $T_0$  through  $T_3$  as follows:

$$T_o: R5 \leftarrow R0$$

$$T_1$$

:  $R5 \leftarrow R1$

$$T_2$$

:  $R5 \leftarrow R2$

$$T_3$$

:  $R5 \leftarrow R3$

The timing variables are mutually exclusive, that is, only one may be equal to 1 at any given time. Draw a block diagram showing the hardware implementation of the register transfers. Include the connections necessary from the four timing variables to the selection inputs of the multiplexers and to the load input of *R5*.

## Q6. Answer the following

- a. How many 128 x 8 RAM chips are needed to provide a memory capacity of 2048 bytes?

- b. How many lines of the address bus must be used to access 2048 bytes of memory?

- c. How many of these lines will be common to all chips?

- d. How many lines must be decode for chip select?

- e. Specify the size of the decoders.

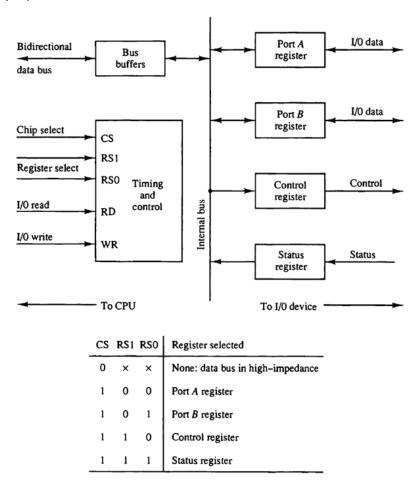

**Q7.** The addresses assigned to the four registers of the I/O interface of the system shown below are equal to the binary equivalent of 12, 13, 14, and 15.

- a. Show the external circuit that must be connected between an 8-bit I/O address from the CPU and the CS, RS1 and RSO inputs of the interface.

- b. Six interface of the type shown in the figure are connected to a CPU that uses an I/O address of 8-bits. Each of the six CS inputs is connected to a different address line. The two low order address lines are connected to the RS1 and RS0 of all six interface units. Determine the 8-bit address of each register in each interface.

- **Q8.** A computer employs RAM chips of 256 x 8 and ROM chips of 1024 x 8. The computer system needs 2K bytes of RAM, 4K bytes of ROM, and four interface units, each with four registers. A memory-mapped I/O configuration is used. The two highest-order bits of the address bus are assigned 00 for RAM and 10 for interface registers.

- a. How many RAM and ROM chips are needed?

- b. Draw a memory-address map for the system.

- c. Give the address range in hexadecimal for RAM, ROM and interface.